INtegrated TOol chain for model-based design of CPSs

## **INTO-CPS Method Guidelines**

Version: 1.7

Date: September 2019

The INTO-CPS Association

http://into-cps.org

#### **Contributors:**

John Fitzgerald, UNEW Carl Gamble, UNEW Martin Mansfield, UNEW Richard Payne, UNEW Ken Pierce, UNEW Peter Gorm Larsen, AU Casper Thule, AU

#### **Editors:**

Ken Pierce, UNEW

# **Document History**

| Ver | Date       | Author            | Description                            |

|-----|------------|-------------------|----------------------------------------|

| 0.1 | 14-02-2017 | Ken Pierce        | Initial document structure             |

| 0.2 | 24-10-2017 | Ken Pierce        | Revised document structure             |

| 0.3 | 26-10-2017 | Ken Pierce        | First draft of materials               |

| 0.4 | 31-10-2017 | Ken Pierce        | Added SysML chapter                    |

| 0.5 | 01-11-2017 | Ken Pierce        | Draft for comment                      |

| 1.0 | 07-12-2017 | Ken Pierce        | First revisions based on comments      |

| 1.1 | 12-12-2017 | Ken Pierce        | Further updates based on comments      |

| 1.2 | 14-12-2017 | Ken Pierce        | Revised SysML chapter                  |

| 1.3 | 18-12-2017 | Carl Gamble       | Traceability chapter completed         |

| 1.4 | 18-12-2017 | Carl Gamble       | DSE chapter completed                  |

| 1.5 | 13-03-2018 | Peter Gorm Larsen | Moved over to the INTO-CPS Association |

| 1.6 | 06-09-2018 | Peter Gorm Larsen | Updated macros                         |

| 1.7 | 27-09-2019 | Casper Thule      | Added CoHLA note                       |

#### **Abstract**

This document is the final methods guidance document for the INTO-CPS technologies. It is aimed at end users of the technologies, and complements the User Manual, [LBL+18], by helping to describe the why to complement the how. This document presents: a concepts base, which describes the terminology used within INTO-CPS; information on getting started with the technologies, and the variety of workflows they support; a description of the traceability features of the tool chain, and why these must be considered at the beginning of development to realise them fully; guidelines on incorporating requirements engineering in a cyber-physical systems (CPS) context; a description of the INTO-SysML profile and its use; guidance on discrete-event first (DE-first) modelling as a way to begin multi-modelling; guidance on modelling networks in multi-models; and guidelines for the use of design space exploration (DSE) features of the INTO-CPS tool chain.

# **Contents**

| Co | Contents                                                |    |  |  |  |  |  |  |

|----|---------------------------------------------------------|----|--|--|--|--|--|--|

| I  | Introductory Material                                   | 7  |  |  |  |  |  |  |

| 1  | Introduction                                            |    |  |  |  |  |  |  |

|    | 1.1 How to Use This Document                            | 8  |  |  |  |  |  |  |

|    | 1.2 Overview of Sections                                | 9  |  |  |  |  |  |  |

| 2  | Concepts and Terminology                                |    |  |  |  |  |  |  |

|    | 2.1 Systems                                             | 11 |  |  |  |  |  |  |

|    | 2.2 Models                                              | 11 |  |  |  |  |  |  |

|    | 2.3 Tools                                               | 13 |  |  |  |  |  |  |

|    | 2.4 Analysis                                            | 14 |  |  |  |  |  |  |

|    | 2.5 Existing Tools and Languages                        | 15 |  |  |  |  |  |  |

|    | 2.6 Formalisms                                          | 16 |  |  |  |  |  |  |

| 3  | Getting Started with INTO-CPS                           |    |  |  |  |  |  |  |

|    | 3.1 Activities Enabled by INTO-CPS                      | 18 |  |  |  |  |  |  |

|    | 3.2 Configuring Multi-Models                            | 21 |  |  |  |  |  |  |

|    | 3.3 First Steps for Users                               | 21 |  |  |  |  |  |  |

| II | Advanced Topics                                         | 23 |  |  |  |  |  |  |

| 4  | raceability and Provenance                              |    |  |  |  |  |  |  |

|    | 4.1 Traceability Workflow                               | 24 |  |  |  |  |  |  |

|    | 4.2 What Artefacts are Traced?                          | 25 |  |  |  |  |  |  |

|    | 4.3 Traceability Queries                                | 28 |  |  |  |  |  |  |

| 5  | equirements Engineering                                 |    |  |  |  |  |  |  |

|    | 5.1 Requirements Engineering and Cyber-Physical Systems | 29 |  |  |  |  |  |  |

|    | 5.2 The SoS-ACRE View of Requirements                   | 30 |  |  |  |  |  |  |

|    | 5.3 The SoS-ACRE RE Process                             | 31 |  |  |  |  |  |  |

|    | 5.4 Using technologies with SoS-ACRE                    | 32 |  |  |  |  |  |  |

| 6  | SysML and Multi-modelling                               | 37 |  |  |  |  |  |  |

|    | 6.1 SysML Diagrams Describing Multi-models              | 37 |  |  |  |  |  |  |

|    | 6.1.1 Architectural Structure Diagram                   | 38 |  |  |  |  |  |  |

|    |        | 6.1.2 Connections Diagram                                        |    |

|----|--------|------------------------------------------------------------------|----|

|    | 6.2    | SysML Diagrams Describing Design Space Exploration               | 39 |

|    |        | 6.2.1 Objective Definition Diagram                               | 39 |

|    |        | 6.2.2 Objective Connection Diagram                               | 40 |

|    |        | 6.2.3 Parameter Definition Diagram                               | 40 |

|    |        | 6.2.4 Parameter Connection Diagram                               | 41 |

|    |        | 6.2.5 Ranking Diagram                                            | 41 |

|    | 6.3    | Holistic and Design Architectural Modelling                      | 41 |

|    | 6.4    | Representing Non-Design Elements in SysML                        | 45 |

| 7  | Initi  | al Multi-Modelling using VDM                                     | 48 |

|    | 7.1    | The DE-first Approach                                            | 48 |

|    | 7.2    | DE-first within INTO-CPS                                         | 50 |

|    | 7.3    | FMU Creation                                                     | 50 |

| 8  | Mod    | lelling Networks with VDM in Multi-models                        | 53 |

|    | 8.1    | Representing VDM Values as Strings                               | 54 |

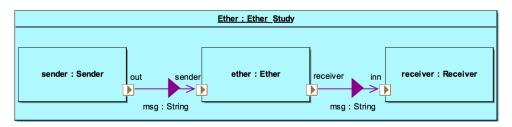

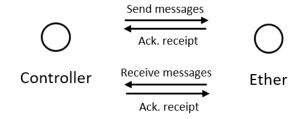

|    | 8.2    | Using the Ether FMU                                              | 54 |

|    | 8.3    | Consequences of Using the Ether                                  | 56 |

|    | 8.4    | Modelling True Message Passing and Quality of Service            | 56 |

| 9  | Desi   | gn Space Exploration                                             | 59 |

|    | 9.1    | Guidelines for Designing DSE in SysML                            | 59 |

|    |        | 9.1.1 Rationale                                                  | 59 |

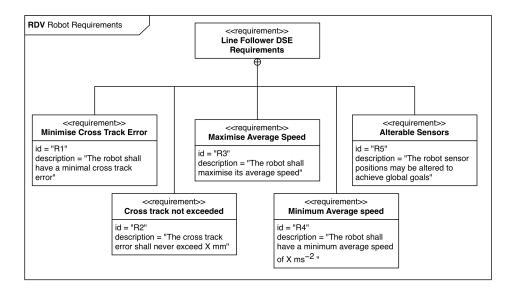

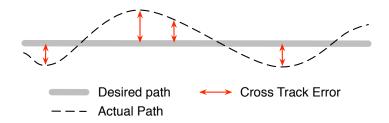

|    |        | 9.1.2 Requirements                                               | 60 |

|    |        | 9.1.3 Objectives from Requirements                               | 60 |

|    |        | 9.1.4 SysML Representation of Parameters, Objectives and Ranking | 61 |

|    |        | 9.1.5 DSE script                                                 | 63 |

|    |        | 9.1.6 DSE results                                                | 63 |

|    | 9.2    | An Approach to Effective DSE                                     | 66 |

|    |        | 9.2.1 A Genetic Algorithm for DSE                                | 67 |

|    |        | 9.2.2 Measuring Effectiveness                                    |    |

|    |        | 9.2.3 Genetic DSE Experiments and Results                        | 69 |

|    |        | 9.2.4 Selecting Approaches based on Design Space                 | 71 |

| Bi | bliogi | raphy                                                            | 74 |

| II | I A    | ppendices                                                        | 79 |

|    | Glos   |                                                                  | 80 |

| A  | CTIOS  | SALV                                                             | ลบ |

# Part I Introductory Material

# Chapter 1

## Introduction

The INTO-CPS tool chain brings together a variety of technologies to allow engineers to undertake collaborative, model-based based design of Cyber-Physical Systems (CPSs). Each technology has its own culture, abstractions, and approaches to problem solving that inform how they are used. Many of these things are tacit and tend to be discovered only after trying to combine them. The guidance in this document aims to help the reader overcome these challenges, and to understand how best to use these technologies.

This document complements the tools User Manual (Deliverable D4.3a [BLL<sup>+</sup>17]) —which gives detail on how to use the features of the tool chain— by providing information on when and why you might use these features. The guidance in this document has been distilled from experience gained in a series of pilot studies and applications of INTO-CPS technologies to real industrial case studies. These pilot studies now appear as examples that can be opened directly from the INTO-CPS Application, supported by descriptions in the Examples Compendium (Deliverable D3.6 [MGP<sup>+</sup>17]). Industrial applications can be read about in the Case Studies report (Deliverable D1.3a [OLF<sup>+</sup>17]).

#### 1.1 How to Use This Document

Since this document is aimed at both new and experienced users of the INTO-CPS technologies, it has been divided into two parts. Part I, Chapters 1–3, covers introductory material including this introduction, the terminology used in INTO-CPS, and the various activities that INTO-CPS enables. Part II, Chapters 4–9, covers more advanced topics that require a basic familiarity with the INTO-CPS technologies.

While the chapters in the Part II are ordered primarily based on a start-to-end "work flow" of system development with INTO-CPS, it is not necessary to read the advanced chapters in order. While experienced users may read any chapter on which they require further guidance, new users are recommended to:

- Read the introductory material in Part I.

- Follow the first tutorial to experience using the INTO-CPS Application.

- Import one or two examples from the Examples Compendium (Deliverable D3.6 [MGP<sup>+</sup>17]) into the INTO-CPS Application and interact with them.

- As you start your own multi-modelling, return to this document as and when you require guidance on a particular area.

#### 1.2 Overview of Sections

- Chapter 2: Concepts and Terminology This chapter is an introduction to the concepts and terminology used in INTO-CPS. It explains many terms from the various baseline technologies, as well as other model-based design terminology. In parts this involved reconciling terms used differently in different areas, and finding common, agreed-upon terms for similar concepts. These concepts are applicable for all documents produced by INTO-CPS (this document, user manuals, deliverables, and publications).

- **Chapter 3: Getting Started with INTO-CPS** This chapter suggests how to get started with the INTO-CPS tool chain, trying out core features by following tutorials, which puts the other range of activities in context. It also describes the full range of activities that the INTO-CPS tool chain enables.

- Chapter 4: Traceability and Provenance This chapter explains how to approach the INTO-CPS tool chain in order to make used of the machine-assisted traceability features included in the INTO-CPS Application and baseline tools. It also describes the set of included queries that can be run over traceability data sets, and how further queries can be written.

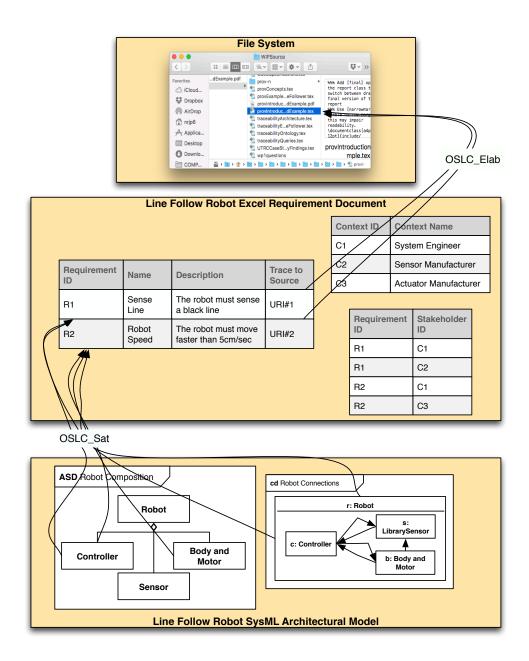

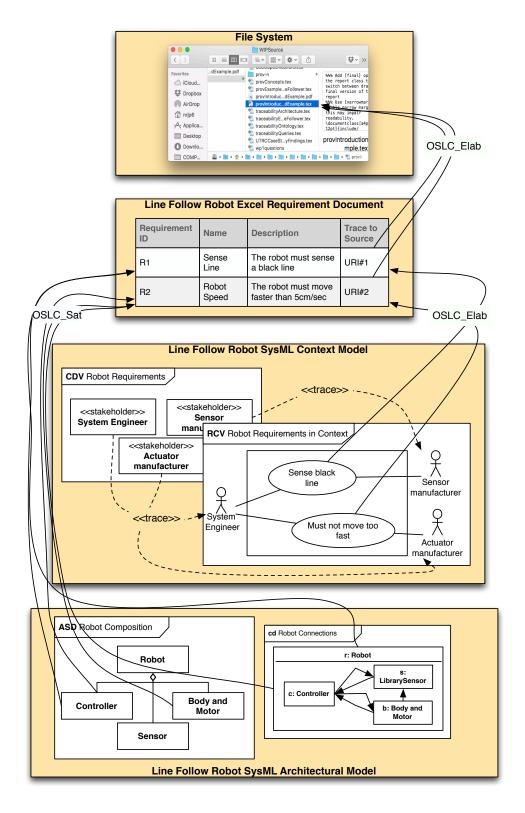

- Chapter 5: Requirements Engineering This chapter focuses on a key initial activity for CPS design, specifically requirements engineering (RE) in a CPS context, and the specification and documentation of requirements placed upon a CPS. This section describes an approach called SoS-ACRE in the context of INTO-CPS, and includes descriptions of how this approach can be realised using tools identified as useful by the industrial partners (specifically SysML and Excel). By following these guidelines, engineers can bridge the gap between natural language requirements and multi-models.

- Chapter 6: SysML and Multi-modelling This chapter describes the various roles of SysML in INTO-CPS. SysML can be used for architectural modelling of CPSs, while INTO-CPS provides additional SysML profiles that can be used to describe the architecture of multi-models and provide machine-assisted configuration of co-simulations and other analyses. This section provides a description of these profiles, how standard SysML can be used within INTO-CPS, and the relationship between these two uses.

- **Chapter 7: Initial Multi-modelling** This chapter looks at producing an initial multi-model through the creation of abstract, discrete-event FMUs. These simplified FMUs can then be replaced by higher-fidelity versions in more appropriate tools such as 20-sim. This is referred to as a "DE-first" approach [FLPV13].

- **Chapter 8: Modelling Networks in Multi-models** This chapter describes how to also model realistic communications between controllers in an FMI setting. This chapter describes one approach: introducing an FMU that represents an abstract communication mechanism, the *ether*. Guidance on the consequences of adopting such an approach is included, as well as extensions to cover quality-of-service modelling.

- **Chapter 9: Design Space Exploration** This chapter gives guidance on DSE, including the types of search algorithms that can be used to explore a design space, and how the SysML profile extensions help in the design of experiments.

This chapter provides information related to the Configuring HLA (CoHLA) domain specific language.

#### **Differences from Previous Versions**

This document builds on previous versions Deliverables D3.1a [FGPP15a] and D3.2a [FGPP16a]). Some material is retained and updated, while other material is entirely new. The following list

gives an overview of new and updated material for each section:

**Concepts and Terminology** appeared in the previous version. The concepts base has been stable in the final year of the project.

**Getting Started with INTO-CPS** has been heavily revised from previous "workflows" section in response to end user interactions and feedback.

Traceability and Provenance is entirely new.

**Requirements Engineering** appeared in the previous version.

**SysML and Multi-modelling** has been updated significantly to present a comprehensive overview of SysML in the INTO-CPS context, using new and revised material.

**Initial Multi-modelling** appeared in the previous version.

Modelling Networks in Multi-models appeared previously.

**Design Space Exploration** has been revised to include description of how to select the algorithm to use and an outline of an iterative search approach.

# Chapter 2

# **Concepts and Terminology**

This section introduces the basic concepts used in the INTO-CPS project. CPSs bring together domain experts from diverse backgrounds, from software engineering to control engineering. Each discipline has developed their own terminologies, principles and philosophy for years — in places they use similar terms for quite different meanings and different terms that have the same meaning. In addition, the INTO-CPS project aims to produce a tool chain for CPS engineering resulting in the need for common tool-based terminology. INTO-CPS requires experts from diverse fields to work collaboratively, so this section gives some core concepts of INTO-CPS that will be used throughout the project. We divide the concepts into several broad areas in the remainder of this section.

## 2.1 Systems

A *System* is defined as being "a combination of interacting elements organized to achieve one or more stated purposes" [INC15]. Any given system will have an *environment*, considered to be everything outside of the system. The behaviour exhibited by the environment is beyond the direct control of the developer [BFG<sup>+</sup>12]. We also define a *system boundary* as being the common frontier between the system and its environment. The definition of the system boundary is application-specific [BFG<sup>+</sup>12].

*Cyber-Physical Systems (CPSs)* refer to "ICT systems (sensing, actuating, computing, communication, etc.) embedded in physical objects, interconnected (including through the Internet) and providing citizens and businesses with a wide range of innovative applications and services" [Tho13, DAB<sup>+</sup>15].

A *System of Systems (SoS)* is a "collection of constituent systems that pool their resources and capabilities together to create a new, more complex system which offers more functionality and performance than simply the sum of the constituent systems" [HIL<sup>+</sup>14]. CPSs may exhibit the characteristics of SoSs.

#### 2.2 Models

In the INTO-CPS project, we concentrate on "model-based design" of CPSs. A *model* is a potentially partial and abstract description of a system, limited to those components and properties of the system that are pertinent to the current goal [HIL+14]. A model should be "just complex enough to describe or study the phenomena that are relevant for our problem context" [vA10]. Models should be abstract "in the sense that aspects of the product not relevant

to the analysis in hand are not included" [FL98]. A model "may contain representations of the system, environment and stimuli" [FLV14]<sup>1</sup>.

In a CPS model, we model systems with cyber, physical and network elements. These components are often drawn from different domains, and are modelled in a variety of languages, with different notations, concepts, levels of abstraction, and semantics, which are not necessarily easily mapped one to another. This heterogeneity presents a significant challenge for simulation in CPSs [HIL+14]. In INTO-CPS we use *continuous time (CT)* and *discrete event (DE)* models to represent physical and cyber elements as appropriate. A CT model has state that can be changed and observed *continuously* [vA10] and is described using either explicit continuous functions of time either implicitly as a solution of differential equations. A DE model has state that can be changed and observed only at fixed, *discrete*, time intervals [vA10]. The approach used in the DESTECS project was to use *co-models* – "a model comprising a DE model, a CT model and a contract" [BFG+12]. In INTO-CPS we propose the use of *multi-models* – "comprising multiple *constituent* DE and CT models". Related to this is a *Hybrid Model*, which contains both DE and CT elements.

A *requirement* may impose restrictions, define system capabilities or identify qualities of a system and should indicate some value or use for the different stockholders of a CPS. *Requirements Engineering (RE)* is the process of the specification and documentation of requirements placed upon a CPS. Requirements may be considered in relation to different *contexts* – that is the point of view of some system component or domain, or interested stakeholder.

We cover the main features of the notations used in INTO-CPS in Section 2.5. Here we consider some general terms used in models. A *design parameter* is a property of a model that can be used to affect the model's behaviour, but remains constant during a given simulation [BFG<sup>+</sup>12]. A *variable* is feature of a model that may change during a given simulation [BFG<sup>+</sup>12]. *Non-functional properties (NFPs)* pertain to characteristics other than functional correctness. For example, reliability, availability, safety and performance of specific functions or services are NFPs that are quantifiable. Other NFPs may be more difficult to measure [PF10].

The activity of creating models may be referred to as *modelling* [FLV14] and related terms include *co-modelling* and *multi-modelling*. A *workflow* is a sequence of *activities* performed to aid in modelling. A workflow has a defined purpose, and may cover a subset of the CPS engineering development lifecycle.

The term *architecture* has many different definitions, and range in scope depending upon the scale of the product being 'architected'. In the INTO-CPS project, we use the simple definition from [PHP+14]: "an architecture defines the major elements of a system, identifies the relationships and interactions between the elements and takes into account process. Those elements are referred to as *components*. An architecture involves both a definition of structure and behaviour. Importantly, architectures are not static but must evolve over time to reflect the change in a system as it evolves to meet changes to its requirements". In a CPS architecture, components may be either *cyber components* or *physical components* corresponding to some functional logic or an entity of the physical world respectively.

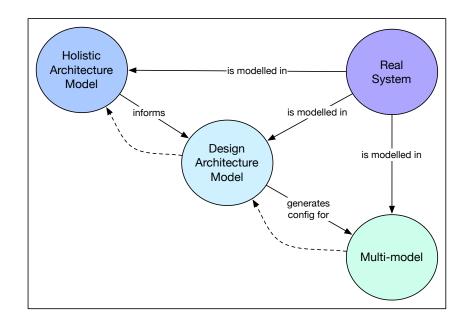

In INTO-CPS we consider both a *holistic architecture* and a *design architecture*. An example of their use is given in Chapter 6. The aim of a holistic architecture is to identify the main

<sup>&</sup>lt;sup>1</sup>Further discussion is required in the final year of INTO-CPS regarding the definition of aspects of models in particular; environment models, test models in RT-Tester and their correspondence in the INTO-CPS SysML profile.

units of functionality of the system reflecting the *terminology and structure of the domain of application*. It describes a conceptual model that highlights the main units of the system architecture and the way these units are connected with each other, taking a holistic view of the overall system. The design architectural model of the system is effectively a multi-model. The INTO-CPS SysML profile [APCB15] is designed to enable the specification of CPS design architectures, which emphasises a decomposition of a system into *subsystems*, where each subsystem is an assembly of cyber and physical components and possibly other subsystems, and modelled separately in isolation using a special notation and tool designed for the domain of the subsystem. *Evolution* refers to the ability of a system to benefit from a varying number of alternative system components and relations, as well as its ability to gain from the adjustments of the individual components' capabilities over time (Adjusted from SoS [NLF+13]).

Considering the interactions between components in a system architecture, an *interface* "defines the boundary across which two entities meet and communicate with each other" [HIL<sup>+</sup>14]. Interfaces may describe both digital and physical interactions: digital interfaces contain descriptions of operations and attributes that are *provided* and *required* by components. Physical interfaces describe the flow of physical matter (for example fluid and electrical power) between components.

There are many methods of describing an architecture. In the INTO-CPS project, an *architecture diagram* refers to the symbolic representation of architectural information contained in a model. An *architectural framework* is a "defined set of viewpoints and an ontology" and "is used to structure an architecture from the point of view of a specific industry, stakeholder role set, or organisation. [HIL+14]. In the application of an architecture framework, an *architectural view* is a "work product (for example an architecture diagram) expressing the architecture of a system from the perspective of specific system concerns" [PHP+14].

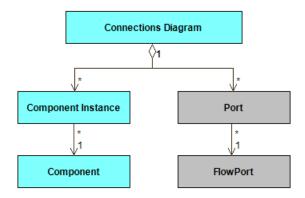

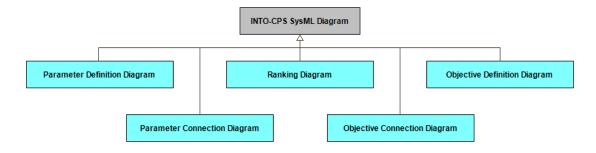

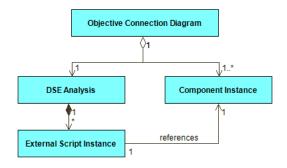

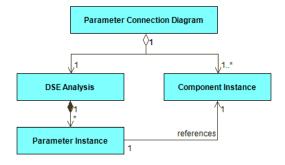

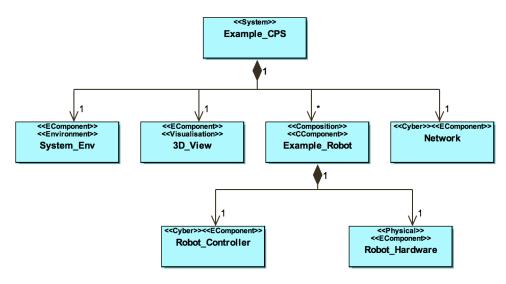

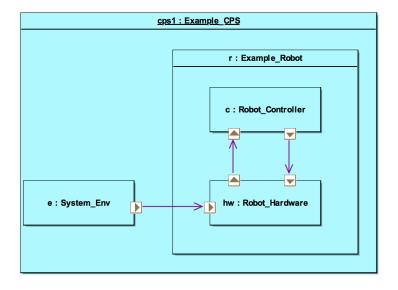

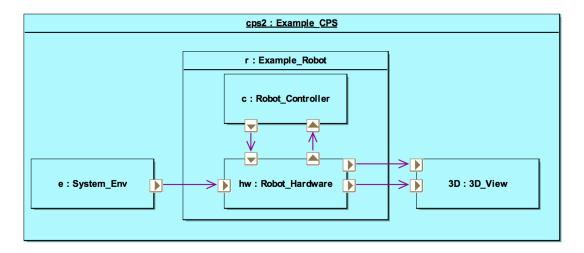

The INTO-CPS SysML profile comprises diagrams for architectural modelling and *design space exploration* specification. There are two architectural diagrams. The *Architecture Structure Diagram* (*ASD*) specialises SysML block definition diagrams to support the specification of a system architecture described in terms of a system's components. *Connections Diagrams* (*CDs*) specialise SysML internal block diagrams to convey the internal configuration of the system's components and the way they are connected. The system architecture defined in the profile should inform a co-simulation multi-model and therefore all components interact through connections between flow ports. The profile permits the specification of *cyber* and *physical* components and also components representing the *environment* and *visualisation* elements. The INTO-CPS SysML profile includes three design space exploration diagrams: a *parameters diagram*; an *objective diagram*; and a *ranking diagram*. See Section 2.4 for concepts relating to design space exploration.

#### **2.3** Tools

The *INTO-CPS tool chain* is a collection of software tools, based centrally around FMI-compatible co-simulation, that supports the collaborative development of CPSs. The *INTO-CPS Application* is a front-end to the INTO-CPS tool chain. The application allows the specification of the co-simulation configuration, and the co-simulation execution itself. The application also provides access to features of the tool chain without an existing user interface (such as design space exploration and model checking). Central to the INTO-CPS tool chain is the use of the Functional Mockup Interface (FMI) standard.

The *Functional Mockup Interface (FMI)* is a tool-independent standard to support both model

exchange and co-simulation of dynamic models using a combination of XML-files and compiled C-code [Blo14]. Part of the FMI standard for model exchange is specification of a *model description* file. This is an XML file that supplies a description of all properties of a model (for example input/output variables). A *Functional Mockup Unit (FMU)* is a tool component that implements FMI. Data exchange between FMUs and the synchronisation of all simulation solvers [Blo14] is controlled by a *Master Algorithm*.

**Co-simulation** is the simultaneous, collaborative, execution of models and allowing information to be shared between them. The models may be CT-only, DE-only or a combination of both. The **Co-simulation Orchestration Engine (COE)** combines existing co-simulation solutions (FMUs) and scales them to the CPS level, allowing CPS multi-models to be evaluated through co-simulation. This means that the COE implements a **Master Algorithm**. The COE will also allow real software and physical elements to participate in co-simulation alongside models, enabling both Hardware-in-the-Loop (HiL) and Software-in-the-Loop (SiL) simulation.

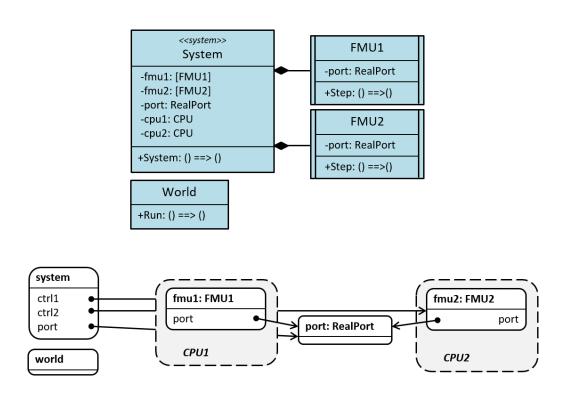

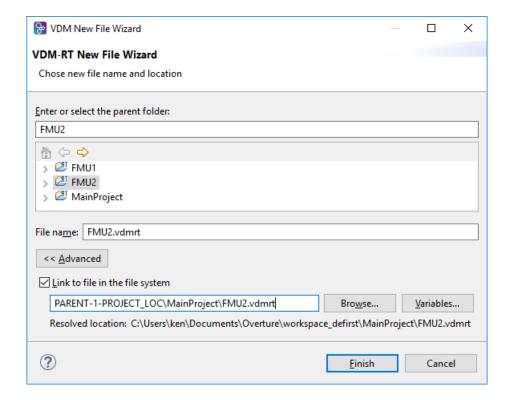

In the INTO-CPS Application, a *project* comprises: a number of FMUs, optional source models (from which FMUs are exported); a collection of *multi-models*; and an optional SysML architectural model. A multi-model includes a list of FMUs, defined instances of those FMUs, specified connections between the inputs/outputs of the FMU instances, and defined values for design parameters of the FMU instances. For each multi-model a *co-simulation configuration* defines the step size configuration, start and end time for the co-simulation of that multi-model. Several configurations can be defined for each multi-model.

*Code generation* is the transformation of a model into generated code suitable for compilation into one or more target languages (e.g. C or Java).

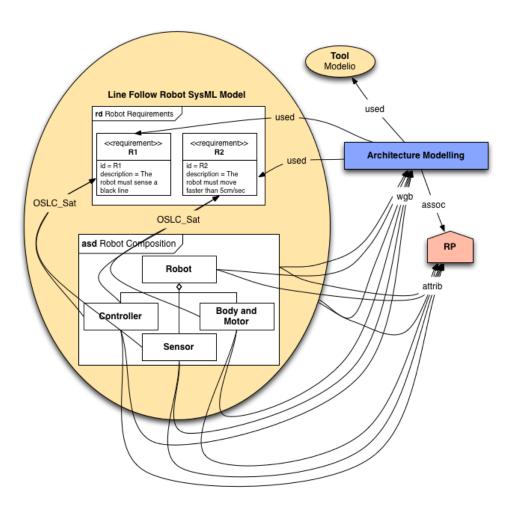

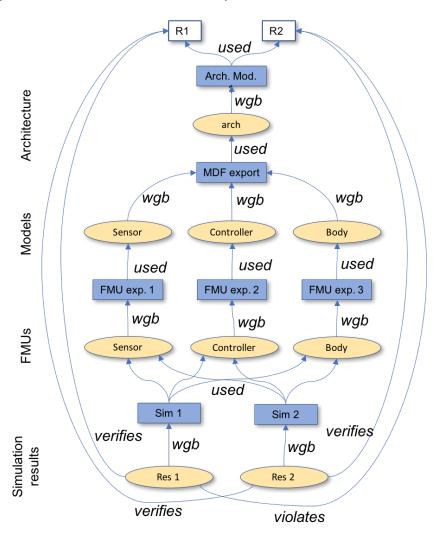

The INTO-CPS project considers two tool-supported methods for recording the rationale of design decisions in CPSs. *Traceability* is the association of one model element (e.g. requirements, design artefacts, activities, software code or hardware) to another. *Requirements traceability* "refers to the ability to describe and follow the life of a requirement, in both a forwards and backwards direction" [GF94]. *Provenance* "is information about entities, activities, and people involved in producing a piece of data or thing, which can be used to form assessments about its quality, reliability or trustworthiness" [MG13]. In INTO-CPS traceability between model elements defined in the various modelling tools is achieved through the use of *OSLC messages*, handled by a traceability *daemon tool*. This supports the *impact analysis* and general *traceability queries*.

Two broad groups of users are considered in the INTO-CPS project. A *Tool Chain User* is an individual who uses the INTO-CPS Tool Chain and its various analysis features. A *Foundations Developer* is someone who uses the developed foundations and associated tool support (see Section 2.6) to reason about the development of tools.

## 2.4 Analysis

**Design-Space Exploration** (**DSE**) is "an activity undertaken by one or more engineers in which they build and evaluate [multi]-models in order to reach a design from a set of requirements" [BFG<sup>+</sup>12]. "The **design space** is the set of possible solutions for a given design problem" [BFG<sup>+</sup>12]. Where two or more models represent different possible solutions to the same problem, these are considered to be **design alternatives**. In INTO-CPS design alternatives are defined using either a range of parameter values or different multi-models. Each choice involves

making a selection from alternatives on the basis of an *objective* – criteria or constraints that are important to the developer, such as cost or performance. The alternative selected at each point constrains the range of design alternatives that may be viable next steps forward from the current position. Given a collection of alternatives with corresponding objective results, a *ranking* may be applied to determine the 'best' design alternative.

**Test Automation** (TA) is defined as the machine assisted automation of system tests. In INTO-CPS, we concentrate on various forms of **model-based testing** – centering on testing system models, against the requirements on the system. The **System Under Test (SUT)** is "the system currently being tested for correct behaviour. An alias for system of interest, from the point of view of the tester" [HIL<sup>+</sup>14]. The SUT is tested against a collection of **test cases** – a finite structure of input and expected output [UPL06], alongside a **test model**, which specifies the expected behaviour of a system under test [CMC<sup>+</sup>13]. TA uses a **test suite** – a collection of **test procedures**. These test procedures are detailed instructions for the set-up and execution of a given set of test cases, and instructions for the evaluation of results of executing the test cases [WG-92].

INTO-CPS considers three main types of test automation: *Hardware-in-the-Loop (HiL)*, *Software-in-the-Loop (SiL)* and *Model-in-the-Loop (MiL)*. In *HiL* there is (target) hardware involved, thus the FMU is mainly a wrapper that interacts (timed) with this hardware; it is perceivable that realisation heavily depends on hardware interfaces and timing properties. In *Software-in-the-Loop (SiL)* testing the object of the test execution is an FMU that contains a software implementation of (parts of) the system. It can be compiled and run on the same machine that the COE runs on and has no (defined) interaction other than the FMU-interface. Finally, in *Model-in-the-Loop (MiL)* the test object of the test execution is a (design) model, represented by one or more FMUs. This is similar to the SiL (if e.g., the SUT is generated from the design model), but MiL can also imply that running the SUT-FMU has a representation on model level; e.g., a playback functionality in the modelling tool could some day be used to visualise a test run.

Model Checking (MC) exhaustively checks whether the model of the system meets its specification [CGP99], which is typically expressed in some temporal logic such as Linear Time Logic (LTL) [Pnu77] or Computation Tree Logic (CTL) [CE81]. As opposed to testing, model checking examines the entire state space of the system and is thus able to provide a correctness proof for the model with respect to its specification. In INTO-CPS, we can concentrate on Bounded Model Checking (BMC) [CBRZ01, CKOS04, CKOS05], which is based on encodings of the system in propositional logic, for a timed variant of LTL. The key idea of this approach is to represent the semantics of the model as a Boolean formula and then apply a Satisfiability Modulo Theory (SMT) [KS08] solver in order to check whether the model satisfies its specification. A powerful feature of model checking is that, if the specification is violated, it provides a counterexample trace that shows exactly how an undesired state of the system can be reached [CV03].

## 2.5 Existing Tools and Languages

The INTO-CPS tool chain uses several existing modelling tools. *Overture*<sup>2</sup> supports modelling and analysis in the design of discrete, typically, computer-based systems using the *VDM-RT* notation. VDM-RT is based upon the *object-oriented* paradigm where a model is comprised of one or more *objects*. An object is an instance of a *class* where a class gives a definition of zero

<sup>&</sup>lt;sup>2</sup>http://overturetool.org/

or more *instance variables* and *operations* an object will contain. Instance variables define the identifiers and types of the data stored within an object, while operations define the behaviours of the object.

The **20-sim**<sup>3</sup> tool can represent continuous time models in a number of ways. The core concept is that of connected **blocks**. **Bond graphs** may implement blocks. Bond graphs offer a domain-independent description of a physical system's dynamics, realised as a directed graph. The vertices of these graphs are idealised descriptions of physical phenomena, with their edges (**bonds**) describing energy exchange between vertices. Blocks may have input and output **ports** that allow data to be passed between them. The energy exchanged in 20-sim is the product of **effort** and **flow**, which map to different concepts in different domains, for example voltage and current in the electrical domain.

*OpenModelica*<sup>4</sup> is an open-source *Modelica*-based modelling and simulation environment. Modelica is an "object-oriented language for modelling of large, complex, and heterogeneous physical systems" [FE98]. Modelica models are described by *schematics*, also called *object diagrams*, which consist of connected components. Components are connected by ports and are defined by sub components or a textual description in the Modelica language.

*Modelio*<sup>5</sup> is an open-source modelling environment supporting industry standards like UML and SysML. INTO-CPS will make use of Modelio for high-level system architecture modelling using the *SysML* language and proposed extensions for CPS modelling. The systems modelling language (SysML) [Sys12] extends a subset of the UML to support modelling of heterogeneous systems.

#### 2.6 Formalisms

The *semantics* of a language describes the meaning of a (grammatically correct) program [NN92] (or model). There are different methods of defining a language semantics: *structural operational semantics*; *denotational semantics*; and *axiomatic semantics*.

A structural operational semantics (SOS) describes how the individual steps of a program are executed on an abstract machine [Plo81]. An SOS definition is akin to an interpreter in that it provides the meaning of the language in terms of relations between beginning and end states. The relations are defined on a per-construct basis. Accompanying the relations are a collection of semantic rules which describe how the end states are achieved. Where an operational semantics defines how a program is executed, a denotational approach defines a language in terms of denotations, in the form of abstract mathematical objects, which represent the semantic function that maps over the inputs and outputs of a program [SS71].

The Unifying Theories of Programming (UTP) [HJ98] is a technique to for describing language semantics in a unified framework. A theory of a language is composed of an *alphabet*, a *signature* and a collection of *healthiness conditions*.

The Communicating Sequential Processes *CSP* notation [Hoa85] is a formal process algebra for describing communication and interaction. *INTO-CSP* is a version of CSP, which will be used to provide a model for the SysML-FMI profile, FMI, VDM-RT and Modelica semantics. It is a front end for a UTP theory of reactive concurrent continuous systems customised for

<sup>3</sup>http://www.20sim.com/

<sup>4</sup>https://www.openmodelica.org/

<sup>5</sup>http://www.modelio.org/

the needs of INTO-CPS. *Hybrid-CSP* is a continuous version of CSP defined originally by He Jifeng [Jif94]. It will be used as a basis to inform the design of INTO-CSP.

Several forms of verification are enabled through the use of formally defined languages. *Refinement* is a verification and formal development technique pioneered by [BW98] and [Mor90]. It is based on a behaviour preserving relation that allows the transformation of an abstract specification into more and more concrete models, potentially leading to an implementation. *Proof* is the process of showing how the validity of one statement is derived from others by applying justified rules of inference [BFL<sup>+</sup>94].

For the purposes of verification in INTO-CPS, and in particular the work of WP2, we make use of the Isabelle/HOL theorem prover and the FDR3 refinement checker. These are not considered part of the INTO-CPS tool chain, and are used in the INTO-CPS project primarily to support the development of foundation work.

# **Chapter 3**

# **Getting Started with INTO-CPS**

This chapter should help you become familiar with the possibilities for collaborative, model-based design offered by the INTO-CPS tool chain. It does this by explaining the types of activities that can be undertaken with support of one or more of the INTO-CPS technologies, and hopefully putting some of the concepts from the previous chapter in context.

Performing one or more of these activities in order, possibly with iterations, forms a "workflow" for using the INTO-CPS technologies. There are many potential workflows, which depend on the users background and intended use for the tools. A key aspect of most workflows is to produce a multi-model, therefore this chapter includes some guidance.

## 3.1 Activities Enabled by INTO-CPS

The following activities are all enabled by one or more of the INTO-CPS technologies. They are grouped into broad categories and include both existing, embedded systems activities and activities enabled by INTO-CPS, since INTO-CPS extends traditional embedded systems design capabilities towards CPS design. The choice of granularity for defining these activities naturally affects the size of such a list. The level chosen is instructive for describing workflows, but one that does not make the described workflows overly long.

In the following descriptions (and corresponding summary in Table 3.1), we identify the tools that support the activities, where applicable, using the following icons:

- The INTO-CPS Application, COE and its extensions.

- Modelio.

- The Overture tool.

- RT-Tester.

- OM OpenModelica.

- 20-sim.

Descriptions of these tools can be found in the concepts base at the beginning of this document in Section 2.5. Those activities in *italics* can be recorded by the traceability features of INTO-CPS, which is described in Chapter 4.

**Requirements and Traceability** Writing *Design Notes* () includes documentation about what has been done during a design, why a decision was made and so on. *Requirements* () includes requirements gathering and analysis. *Validation* () is any form of validation of a design or implementation against its required behaviour.

**Architectural Modelling** INTO-CPS primarily supports architectural modelling in SysML. *Holistic Architectural Modelling* ( and *Design Architectural Modelling* ( are described in Section 6. The former focuses on a domain-specific view, whereas the latter targets multimodelling using a special SysML profile. The *Export Model Descriptions* ( activity indicated passing component descriptions from the Design Architectural Model to other modelling tools.

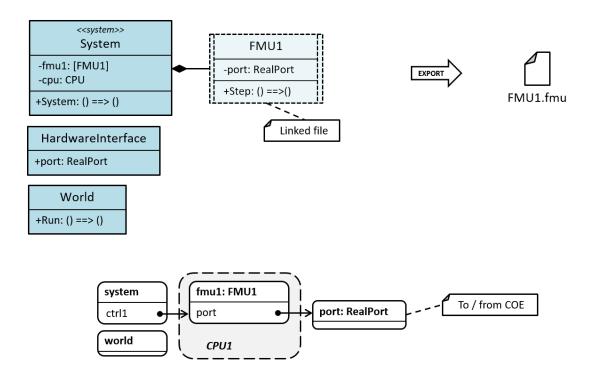

Modelling The Import Model Description ( Model into another modelling a component interface description from the Design Architectural Model into another modelling tool. Cyber Modelling ( man capturing a "cyber" component of the system, e.g. using a formalism/tool such as VDM/Overture. Physical Modelling ( Modelling (

**Design** Supervisory Control Design means designing some control logic that deals with high-level such as modal behaviour or error detection and recovery. Low Level Control Design means designing control loops that control physical processes, e.g. PID control. Software Design is the activity of designing any form of software (whether or not modelling is used). Hardware Design means designing physical components (whether or not modelling is used).

Analysis In INTO-CPS, the RT-Tester tool enables the activities of *Model Checking* (), *Creating Tests* () and creating a *Test Oracle* () FMU. The *Create a Configuration* () activity means preparing a multi-model for co-simulation. The *Define Design Space Exploration Configurations* () activity means preparing a multi-model for multiple simulations. *Export FMU* () means to generate an FMU from a model of a component. *Cosimulation* () means simulating a co-model, e.g. using Crescendo baseline technology or the COE.

**Prototyping** Manual Code Writing means creating code for some cyber component by hand. Generate Code ( Manual Code Writing means to automatically create code from a model of a cyber component. Hardware-in-the-Loop (HiL) Simulation ( ) and Software-in-the-Loop (HiL) Simulation ( ) mean simulating a multi-model with one or more of the models replaced by real code or hardware.

Table 3.1: Activities in existing embedded systems design workflows or enhanced INTO-CPS workflows.

| Requirements Engineering                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stakeholder Documents                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Requirement Definition                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Validation                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Architectural Modelling                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Holistic Architectural Modelling               | <b>(</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Design Architectural Modelling                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Export Model Descriptions                      | <b>(a)</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Modelling                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Import a Model Description                     | Second Seco |

| Physical Modelling (Simulation Modelling)      | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Cyber Modelling (Simulation Modelling)         | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Co-modelling                                   | 0=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Multi-modelling                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Design                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

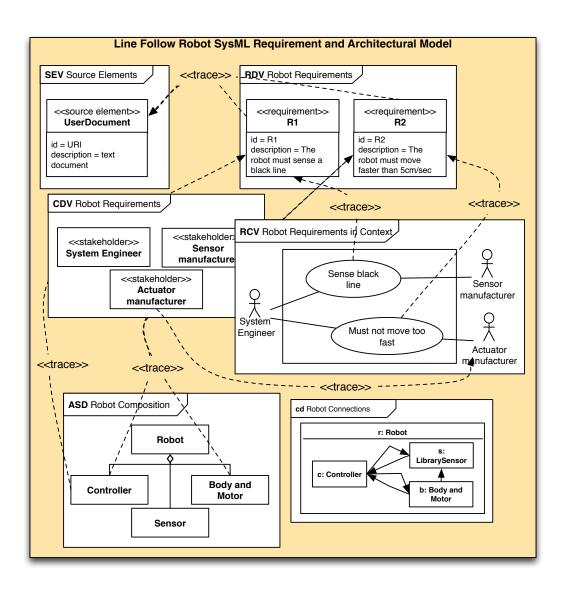

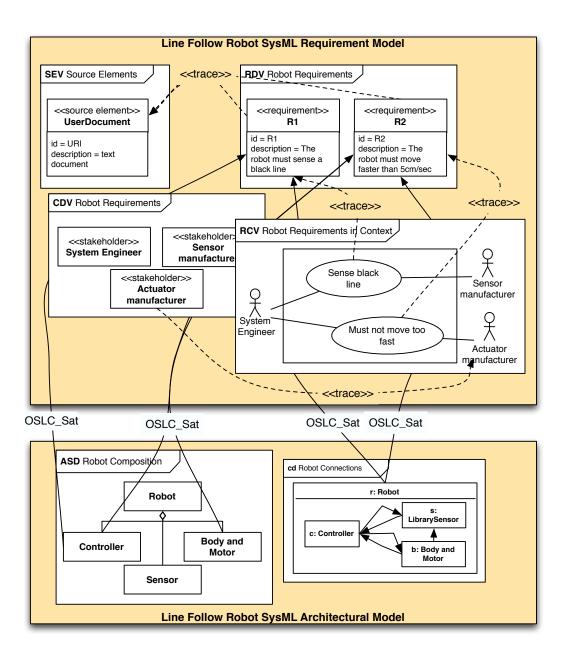

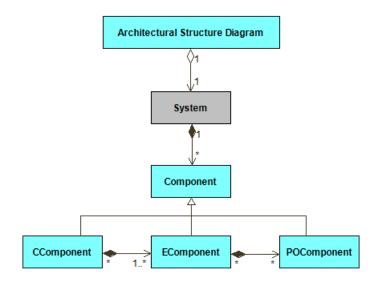

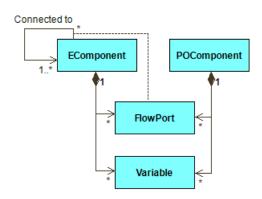

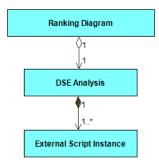

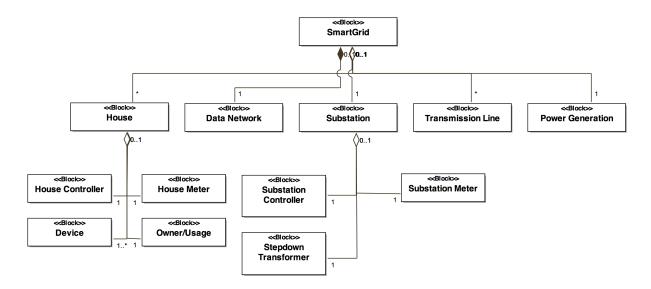

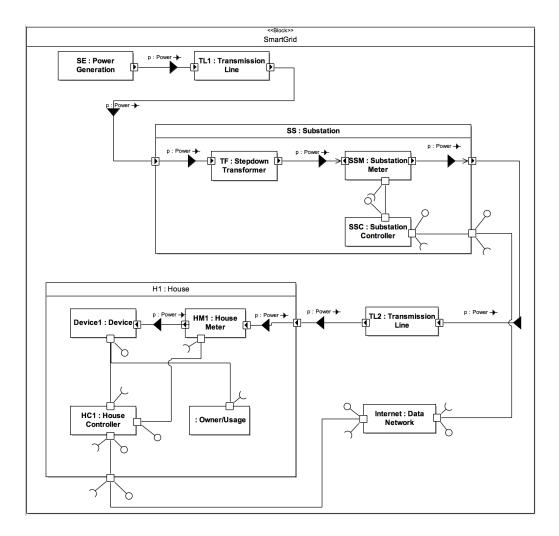

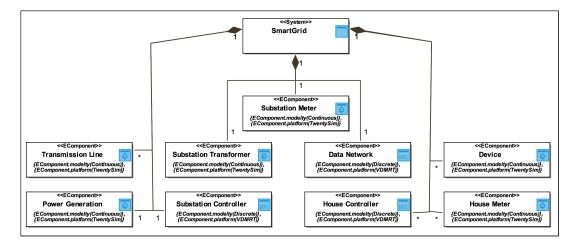

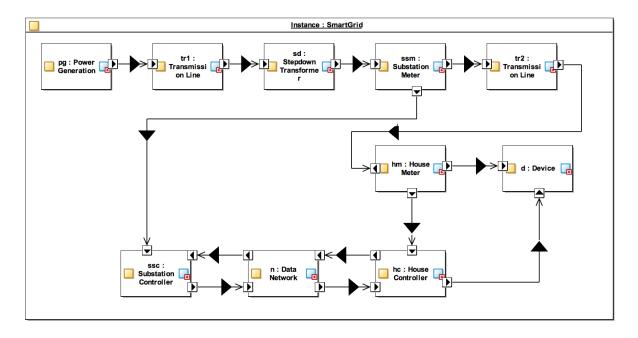

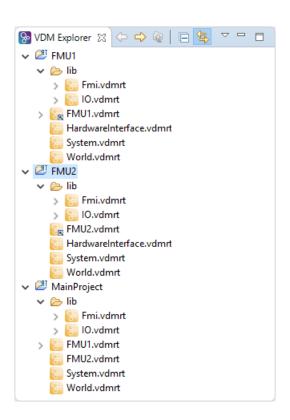

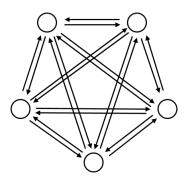

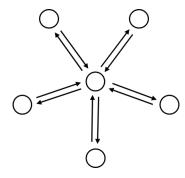

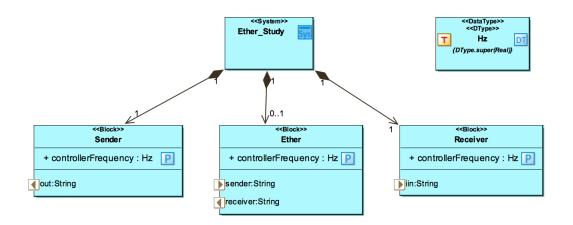

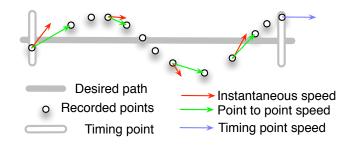

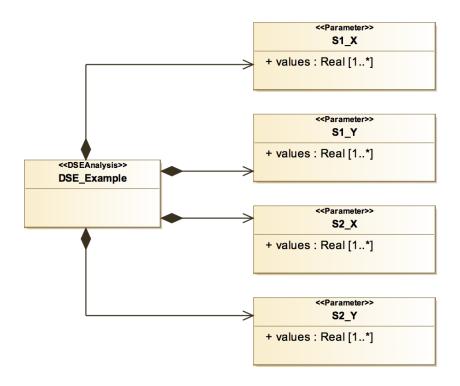

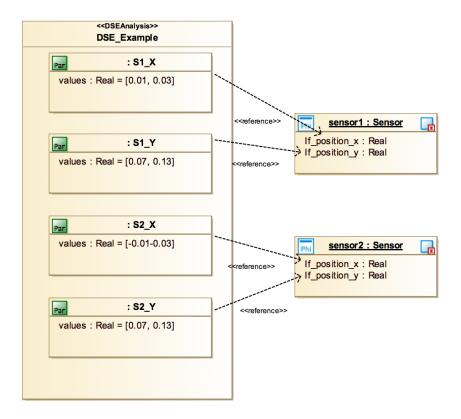

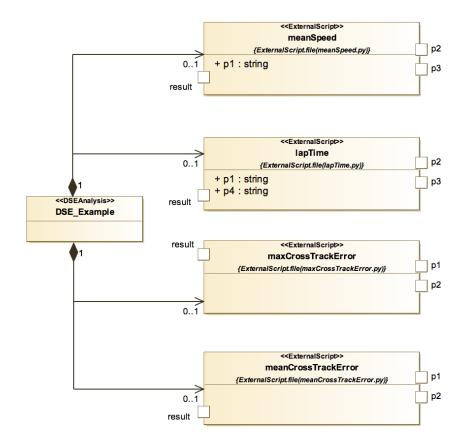

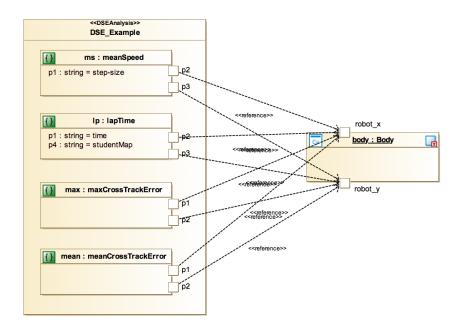

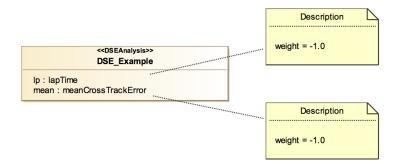

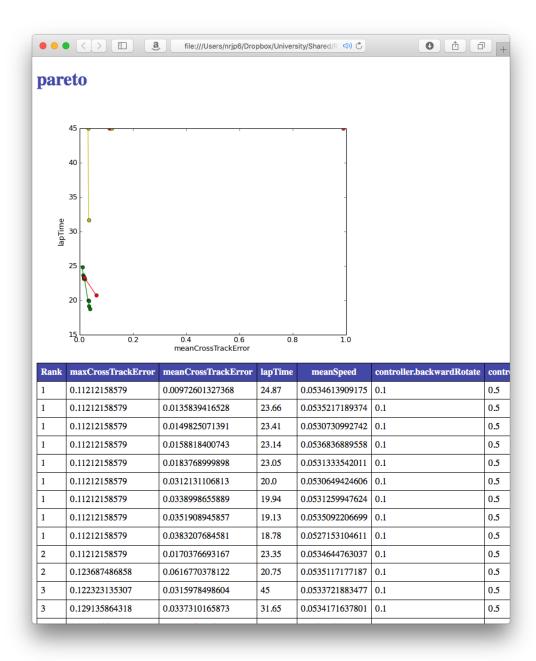

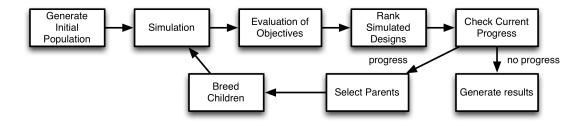

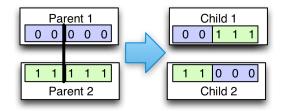

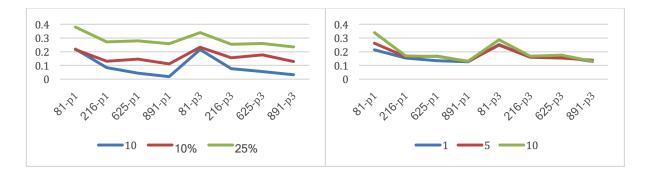

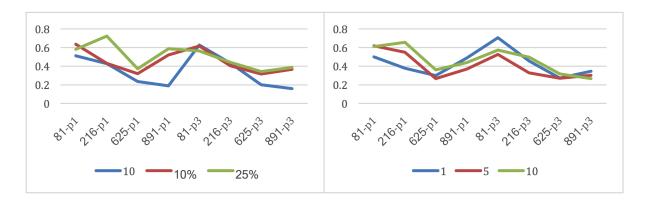

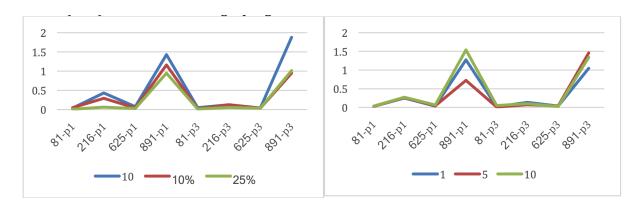

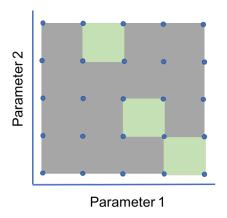

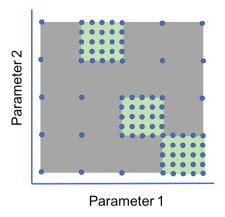

| Supervisory Controller Design                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |